Industry Tutorial: Low Loss Photonic Integrated Circuits: From Prototype to Volume

07 December 2023 11:00 - 12:00

Eastern Time (US & Canada) (UTC -05:00)

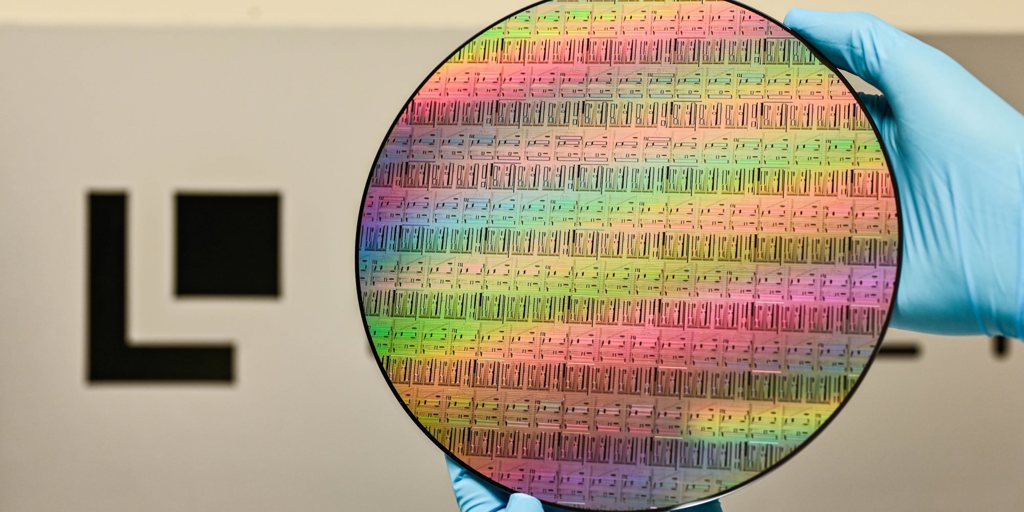

In this talk, we present progress on scaling the fabrication of low loss photonics integrated circuits to volume. We will discuss application spaces ranging from sensing to optical computing, including quantum computing and telecommunication, where low loss PICs are crucial to enable a technology breakthrough. Options of active integration, such as LNOI are discussed to get high speed modulation on a low loss platform. We create the bridge from fast R&D cycles in low volume PIC fabrication through multi-project wafer runs to high volume PIC fabrication in an automotive qualified CMOS line

Speakers

Michael Geiselmann

LIGENTEC, CCO

Michael Geiselmann (CCO) studied physics and engineering at University Stuttgart and Ecole Centrale Paris. After his PhD at ICFO in Barcelona in 2014 he joined the laboratory of Prof. Kippenberg at EPFL in Lausanne, where he advanced frequency comb generation on integrated silicon nitride chips towards applications and was involved in several international research projects. In 2016, he co-founded LIGENTEC and brought the company to the international stage of photonic integration.